# **Ch.3 Input and Output**

#### Topics

- Introduction: input and output (I/O)

- Gaming industry devices

- → 3.1.1: I/O device system interface

- 3.1.2: Program-controlled I/O transfer

- 3.2: Interrupt-based I/O

- 3.2.6: Exceptions

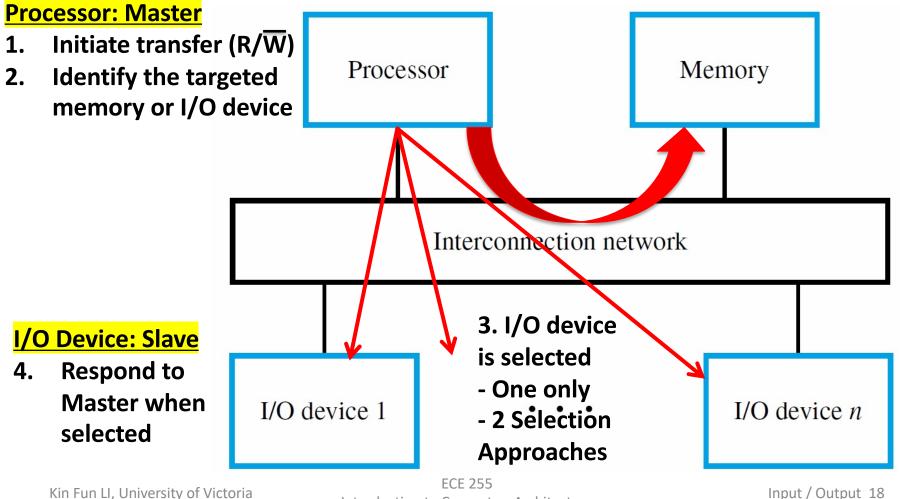

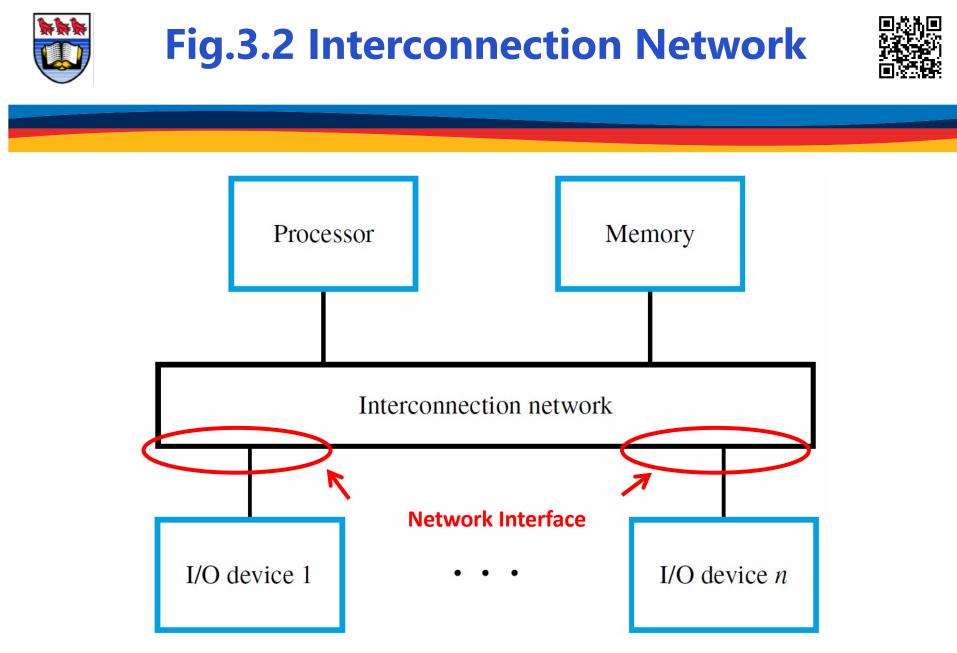

## **Fig.3.2 Interconnection Network**

Introduction to Computer Architecture

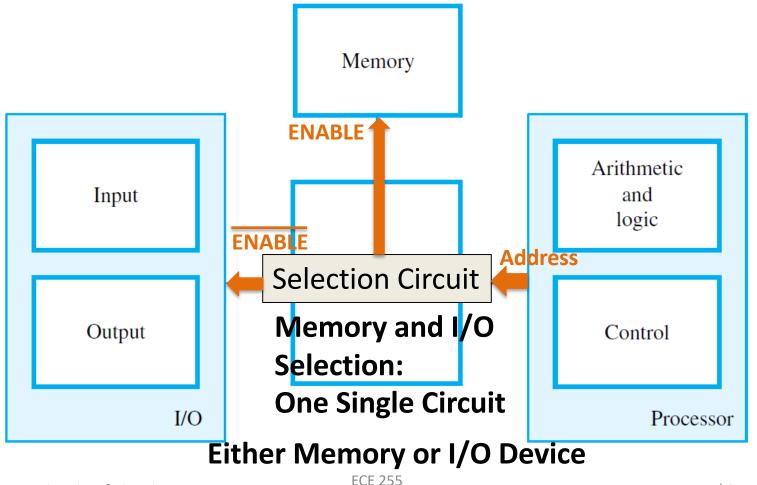

### Selecting I/O Method 1: Memory-Mapped

Kin Fun LI, University of Victoria

Introduction to Computer Architecture

Locations of I/O device's <u>registers</u> are in the same address space as memory

| Binary |    |    | Integer |          |

|--------|----|----|---------|----------|

| A2     | A1 | A0 | Memory  | I/O      |

| 0      | 0  | 0  | 0       |          |

| 0      | 0  | 1  | 1       |          |

| 0      | 1  | 0  | 2       |          |

| 0      | 1  | 1  | 3       |          |

| 1      | 0  | 0  | 4       |          |

| 1      | 0  | 1  | 5       |          |

| 1      | 1  | 0  |         | Input-1  |

| 1      | 1  | 1  |         | Output-1 |

- Use Load and Store (RISC), or Move (CISC) instructions

- Output: Move R0, Output-1 (Output-1=%111=7)

- Input: Load Input-1, R1 (Input1=%110=6)

- Memory addresses: [0..5] (note: 2 less memory locations for user)

Kin Fun LI, University of Victoria

ECE 255 Introduction to Computer Architecture

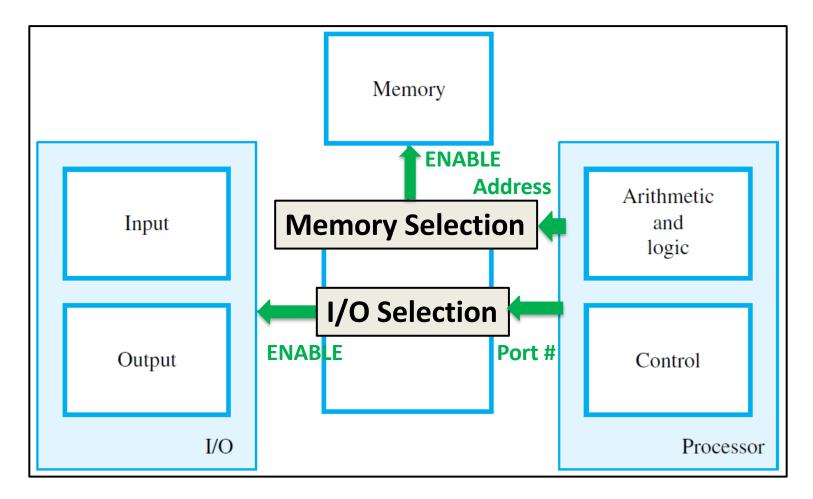

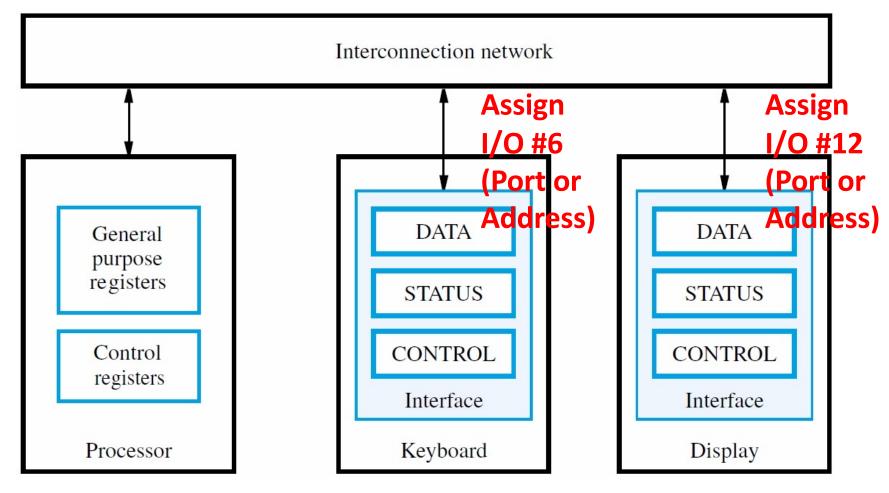

### Selecting I/O Method 2: I/O-Mapped

Kin Fun LI, University of Victoria

ECE 255 Introduction to Computer Architecture

- Each I/O device and its registers are assigned a distinct "I/O address space" or "Ports"

- Use special I/O instructions (i.e., more instructions in ISA!)

- Output: Output R6, OutPort1 ; OutPort1  $\leftarrow$  R6

- Input: Input InPort1, R5 ; InPort1  $\leftarrow$  R5

- Need additional circuit to select (i.e., more hardware!)

- BUT Full memory space is available (vs Memory-mapped)

Kin Fun LI, University of Victoria

ECE 255 Introduction to Computer Architecture

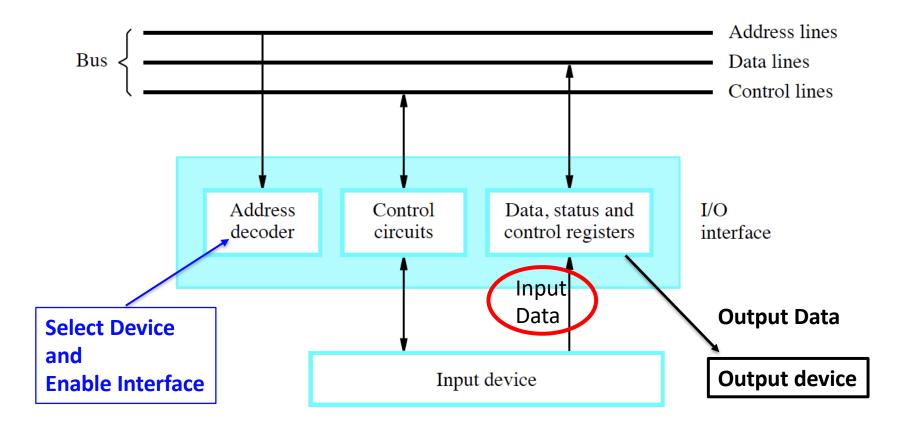

### 3.1.1 I/O Device-Network Interface

- Interconnection Network = System Bus

- Data

- Number of signals or lines = word size (16, 32, 64 etc.)

- Address

- S Number of signals or lines <u>often</u> = word size

- Control Number of signals or lines depends on the CPU design

- Network Interface:

- An electronic circuit

- Between a device and the network

- Provides control, data transfer, and status information to/from the device

Kin Fun LI, University of Victoria

# Fig. 3.2 Network Interface

Kin Fun Ll, University of Victoria

ECE 255 Introduction to Computer Architecture

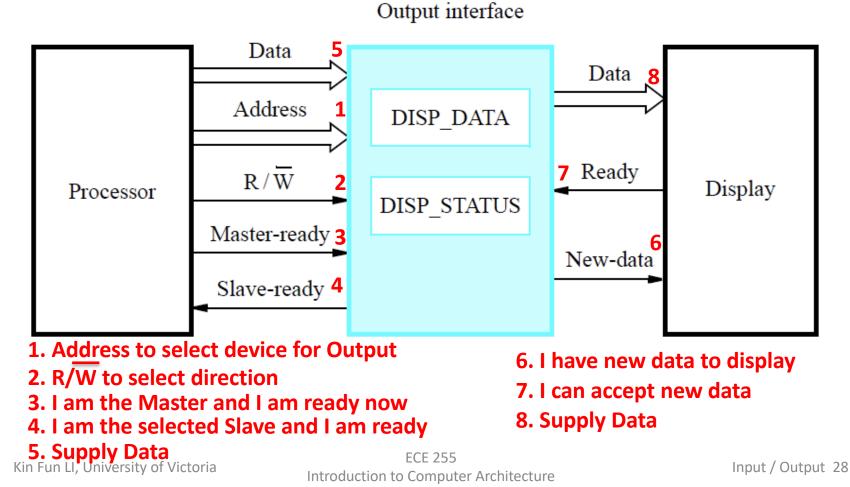

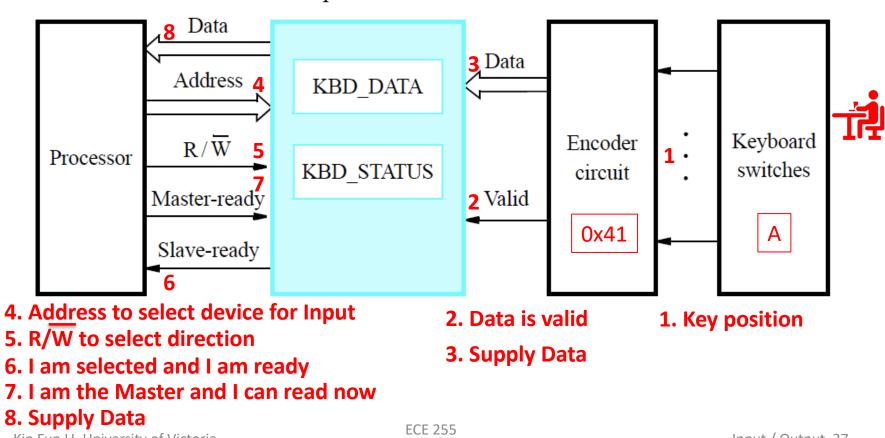

#### Signal Sequence: 1,2...7 in order (a handshaking protocol example)

Input interface

Kin Fun LI, University of Victoria

ECE 255 Introduction to Computer Architecture

#### Signal Sequence: 1,2...7 in order (a handshaking protocol example)